An AI just designed a working CPU — in 12 hours, with zero humans

Design Conductor autonomously built a 1.5 GHz RISC-V chip from a 219-word prompt to tape-out in 12 hours — a world first that could compress chip design from years to days.

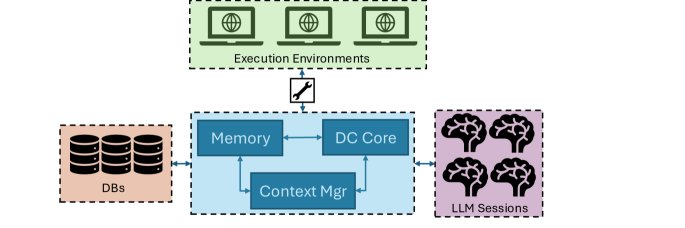

A team of three researchers just demonstrated something the semiconductor industry has never seen: an AI agent that took a one-paragraph description of what a chip should do, and autonomously designed an entire working CPU — from initial architecture to final manufacturing-ready layout — in just 12 hours.

No human touched the design. No engineer reviewed the code mid-process. The AI agent, called Design Conductor, read a 219-word requirements document and produced a complete RISC-V processor (a type of open-standard chip design used in everything from smartphones to servers) that runs at 1.48 GHz — roughly matching an Intel Celeron from 2011.

From a paragraph to a physical chip — every step automated

What makes this different from previous AI-assisted chip design is the scope. Design Conductor didn't just help with one step — it handled the entire pipeline:

The 8-step autonomous process:

1. Read the 219-word spec and stored it in memory

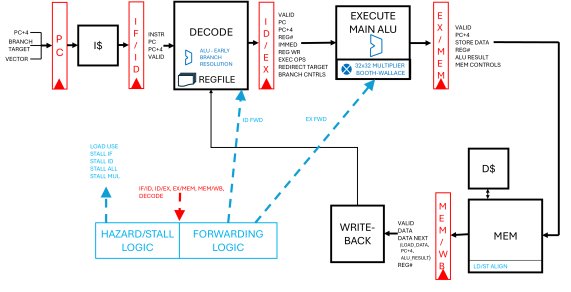

2. Generated its own architectural proposal (pipeline stages, hazard handling, branch logic)

3. Reviewed its own design — cycle by cycle

4. Wrote the hardware description code (Verilog), module by module

5. Created its own tests for each module

6. Debugged failures by analyzing signal waveforms

7. Optimized timing to hit the 1.48 GHz target

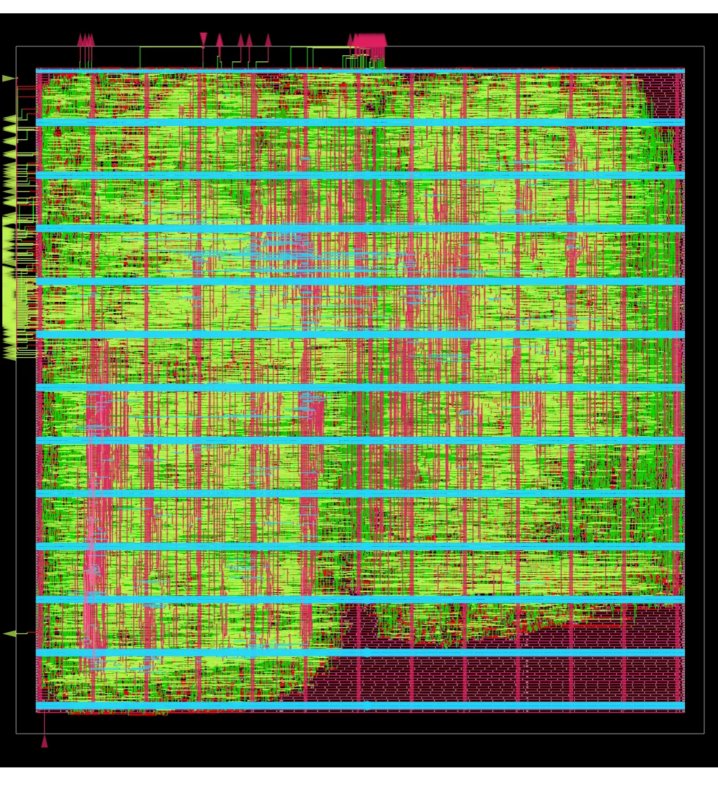

8. Ran the full physical layout flow — producing a file manufacturers can use to print the chip

The resulting chip, dubbed VerCore, scored 3,261 on CoreMark (a standard CPU performance test), putting it in the same ballpark as Intel's Celeron SU2300 from 2011. That's not cutting-edge by today's standards, but the point isn't speed — it's that no human was involved at any point.

Why chip designers should pay attention — not panic

Designing a modern chip typically takes 18 to 36 months with teams of dozens of engineers. The researchers behind Design Conductor believe their approach could compress that to 3 to 6 months — not by replacing engineers, but by letting small teams explore multiple design variations simultaneously.

The paper is refreshingly honest about what the AI still gets wrong:

Where frontier AI models still struggle with chip design:

• They sometimes treat Verilog (hardware description language) like regular software code — leading to timing errors

• Without extremely precise specs, the AI makes suboptimal architectural choices

• Complex forwarding logic (a CPU optimization technique) still needed AI-driven trial-and-error to get right

The researchers emphasize that human architects remain essential — but their role shifts from writing code to guiding the AI at the strategic level. Think of it like the difference between driving a car and telling a self-driving car where to go.

The bigger picture: custom chips could become affordable

Right now, custom chip design is so expensive that only the largest companies can afford it. If an AI agent can produce working designs in hours instead of years, it opens the door to custom silicon for niche applications — specialized chips for medical devices, agricultural sensors, or industrial equipment that were previously too low-volume to justify the engineering cost.

The paper envisions a future where a senior engineer gives Design Conductor a spec in the morning, reviews multiple completed design variants by evening, and picks the best one — a workflow that currently takes an entire team months to achieve.

The technical details

Chip name: VerCore

Architecture: RISC-V (rv32i-zmmul), 5-stage in-order pipeline

Clock speed: 1.48 GHz

Technology node: ASAP 7nm

Die area: 70 µm × 70 µm (excluding cache)

CoreMark score: 3,261

Design time: 12 hours, fully autonomous

Input: 219-word requirements document

Created by: Ravi Krishna, Suresh Krishna, David Chin (Verkor Team)

The full paper is available on arXiv. Design Conductor is not currently open-source, but the detailed methodology in the paper gives other teams a roadmap to replicate the approach.

Related Content — Get Started with Easy Claude Code | Free Learning Guides | More AI News

Stay updated on AI news

Simple explanations of the latest AI developments